應用這 Foverus 設計的最大好處,是可讓 Intel 能在更小的空間裡置放更多的電晶體,更具效率地使用空間。雖然 Intel 沒有透露會由什麼產品搶先搭載這處理器,但大概會是同時主打高效、輕薄的裝置吧。

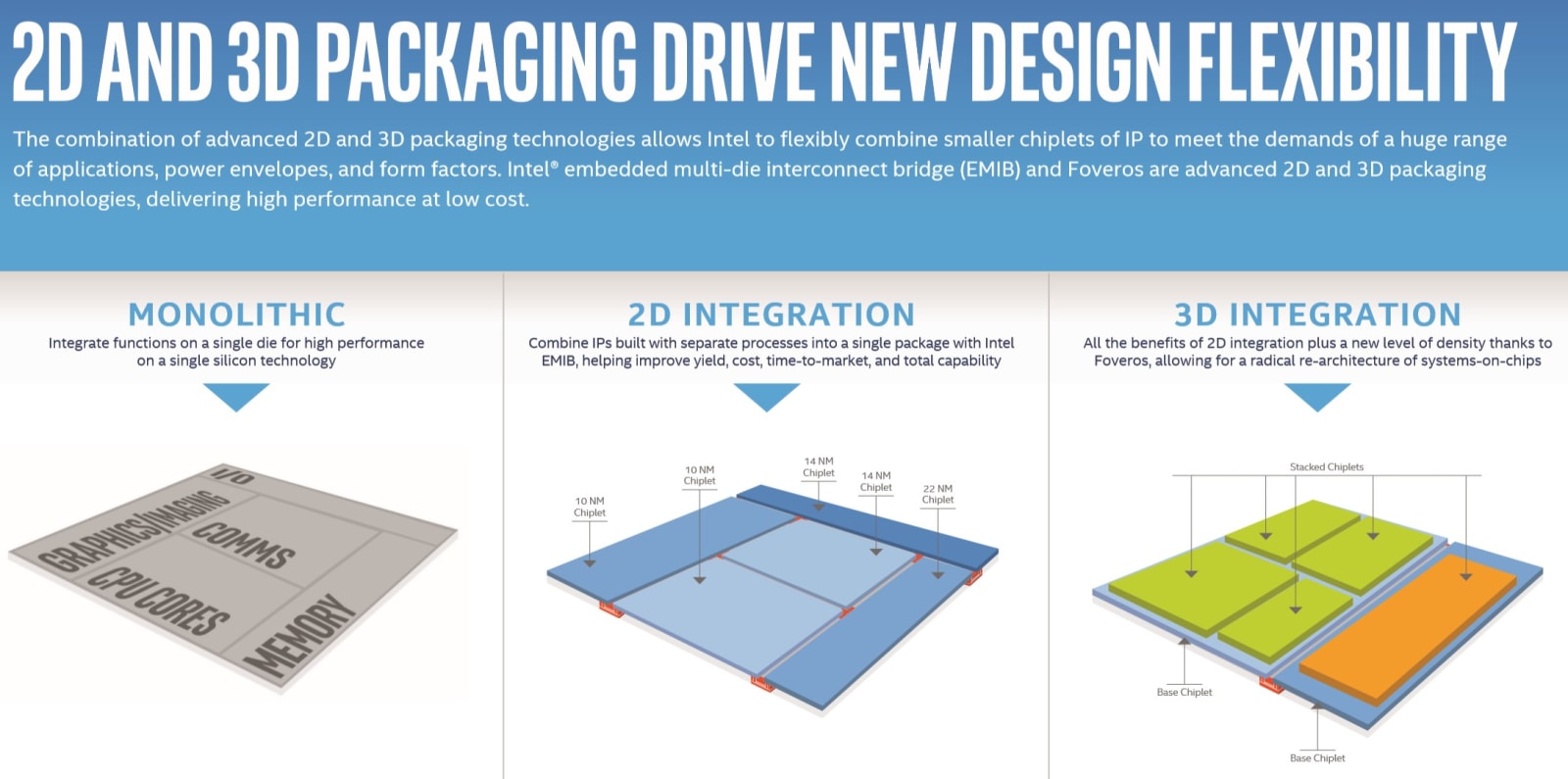

能在一片晶片上擺放電晶體的空間變得愈來愈有限,意味著我們正面臨摩爾定律的尾聲,所以下一步就只可以往上發展。隨著 Intel 最新的發表,我們正式步進 3D 結構的晶片年代--Intel 開發了一個可以把多個邏輯晶片,諸如 CPU 和 GPU 堆棧擺放。這可不是研究項目,Intel 表示我們最快可在明年下半年就看到首批應用這「Foverus」架構的產品。

雖說像 AMD 的 R9 Fury X 就是應用了類似的 3D 堆棧式架構來設計的高頻寬記憶體(設計師正是轉投到 Intel ,負責領導新的核心與視覺運算事業群的 Raja Koduri),但這 Foverus 架構卻是再上一層樓,據 Intel 的說法是可用予更細小的「晶片組」之上,即位於基本晶片頂部的快速邏輯晶片,主於負責電源、I/O、電力傳輸等工作。首個應用 Foverus 架構的產品更會是 10nm 製程的運算元件,定位將會是低功耗產品。

應用這 Foverus 設計的最大好處,是可讓 Intel 能在更小的空間裡置放更多的電晶體,更具效率地使用空間。雖然 Intel 沒有透露會由什麼產品搶先搭載這處理器,但大概會是同時主打高效、輕薄的裝置吧。

轉載來源為: Engadget 新聞網

| 歡迎光臨 伊莉討論區 (http://www05.eyny.com/) | Powered by Discuz! |